Flip-flop là một phần tử nhớ trong kỹ thuật vi mạch điện tử có hai trạng thái bền và được sử dụng để lưu trữ thông tin trạng thái.

R1, R2 = 1 kΩ R3, R4 = 10 kΩ).Minh họa hoạt động giải trí của chốt SR ( = 1 kΩ = 10 kΩ ) .

R1, R2 = 1 kΩ R3, R4 = 10 kΩ).Minh họa hoạt động giải trí của chốt SR ( = 1 kΩ = 10 kΩ ) .

Một flip-flop (thường viết tắt trong sơ đồ là f/f hay f-f) là một đa hài ổn định kép.

Mạch này thực hiện xử lý trạng thái của tín hiệu của một hoặc nhiều ngõ vào và cho kết quả ở ngõ ra. Đây là yếu tố cơ bản lưu trữ trong logic tuần tự. Flip-flop và chốt (latch) là vật liệu xây dựng cơ bản của các hệ thống thiết bị điện tử kỹ thuật số, được sử dụng trong các máy tính, truyền thông, và nhiều loại khác của hệ thống điều khiển.[1]

Bạn đang đọc: Flip-flop – Wikipedia tiếng Việt

Flip-flop được sản xuất thành IC tự lập hoặc là thành phần tích hợp trong những IC khác .

Mục lục nội dung

Nguyên lý hoạt động giải trí[sửa|sửa mã nguồn]

Flip-flop thực hiện chức năng xử lý tín hiệu vào và làm 1 bít nhớ trạng thái kết quả, với hai ngõ ra là thuận Q và đảo Q.[2]

Nhu cầu điều khiển và tinh chỉnh dẫn đến chế ra Flip-flop hoàn toàn có thể có nhiều ngõ vào và phương pháp tác động ảnh hưởng của ngõ lên tác dụng khác nhau. Theo quy tắc chung, những ngõ vào chia ra ba loại :

- Ngõ vào dữ liệu D (Data): Trị logic hay trạng thái chính cần chốt.

- Ngõ vào điều khiển không đồng bộ: Khi ngõ khiển này ở mức tích cực (active) thì Flip-flop hoạt động theo cách nào đó. Ngõ này thường ký hiệu là E hay EN (enable) hay gate. Mức tích cực do nhà chế tạo đặt ra, có thể là logic 1 (thuận) hay 0 (đảo).

- Ngõ vào clock hay nhịp đồng bộ CLK: Có ở các Flip-flop cần hoạt động đồng bộ. Flip-flop thực hiện chức năng chính của nó vào thời điểm sườn xung clock chuyển từ 0 lên mức cao. Quy ước này được tất cả nhà sản xuất tôn trọng.

Trong những ngõ khiển, thì R ( Reset ) thường nhắc đến nhiều nhất, nó Reset cho Q. trong f / f về trị logic 0, Q. về trị logic 1. Chú ý rằng Reset là tín hiệu sử dụng trong mọi mạng lưới hệ thống digital, nhưng ở đó từng nơi nó hoàn toàn có thể đặt trị mặc định là 1 khi thiết yếu .

Trong sử dụng phải tránh Xung đột do các ngõ khiển gây ra bất định kết quả, tức là phải thiết kế timing đúng, và các ngõ khiển không dùng đến thì phải nối vào nơi có mức logic không tích cực (inactive).

Các đặc trưng hoạt động giải trí[sửa|sửa mã nguồn]

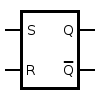

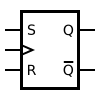

Flip-flop RS hay Flip-flop SR [2] là một đa hài đợi, đơn giản nhất, có 2 ngõ vào R (Reset) và S (Set). R và S ngược nhau và xung đột nhau.

F / f RS được tích hợp làm ngõ khiển trong nhiều f / f còn lại .

Flip-flop RSH [2] là f/f RS có thêm ngõ khiển EN hay Gate. Khi EN là active thì mở cho R hay S tác động.

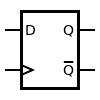

Flip-flop D-type [3] là f/f đồng bộ, khi CLK tác động thì dữ liệu D (Data) chuyển tới ngõ ra Q.

Flip-flop RS

Flip-flop RSH

Flip-flop D (simple)

Flip-flop D

Flip-flop JK (simple)

Flip-flop JK

Flip-flop D

Flip-flop T

Flip-flop JK [4] là f/f đồng bộ. Nó xử lý gần như f/f RS khi coi (J=Set, K=Reset) và giải thích sự kiện:

Xem thêm: New York Yankees – Wikipedia tiếng Việt

- J = 1, K = 0 là lệnh Set

- J = 0, K = 1 là lệnh Reset

- J = 1, K = 1 là lệnh “flip” hay toggle.

Hoạt động flip-flop JK

Characteristic table

Excitation table

J

K

Comment

Qnext

Q

Qnext

Comment

J

K

0

0

hold state

Q

0

0

No Change

0

X

0

1

reset

0

0

1

Set

1

X

1

0

set

1

1

0

Reset

X

1

1

1

toggle

Q.

1

1

No Change

X

0

Flip-flop T [5] hay f/f Toggle, thực hiện Đổi ngược ngõ ra khi có:

- T chuyển sang active

- Khi T là inactive thì khi CLK tác động.

Liên kết ngoài[sửa|sửa mã nguồn]

Source: https://blogchiase247.net

Category: Hỏi Đáp